NXP Imx6

-

Payment

-

Origin

China Mainland

-

Minimum Order

5

-

Packing

Pieces

- Contact Now Start Order

- Description

Product Detail

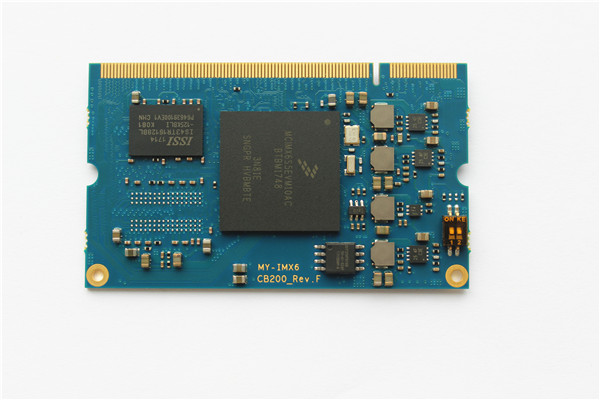

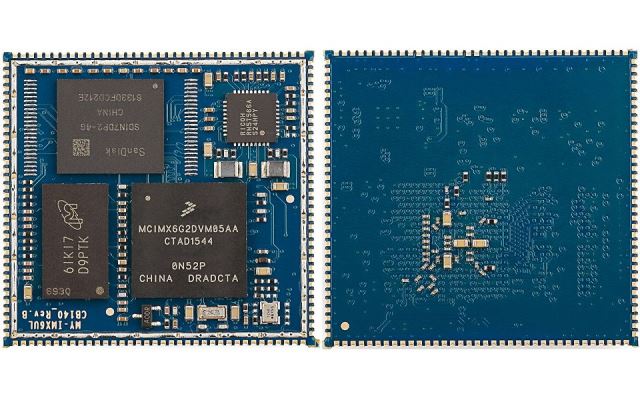

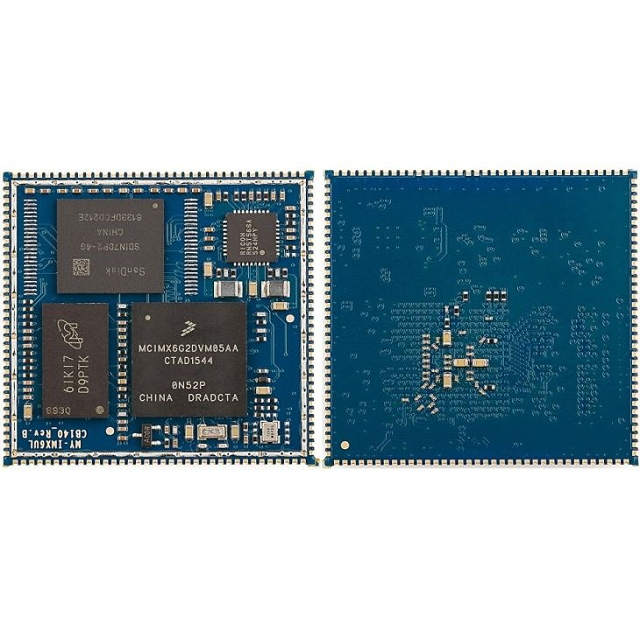

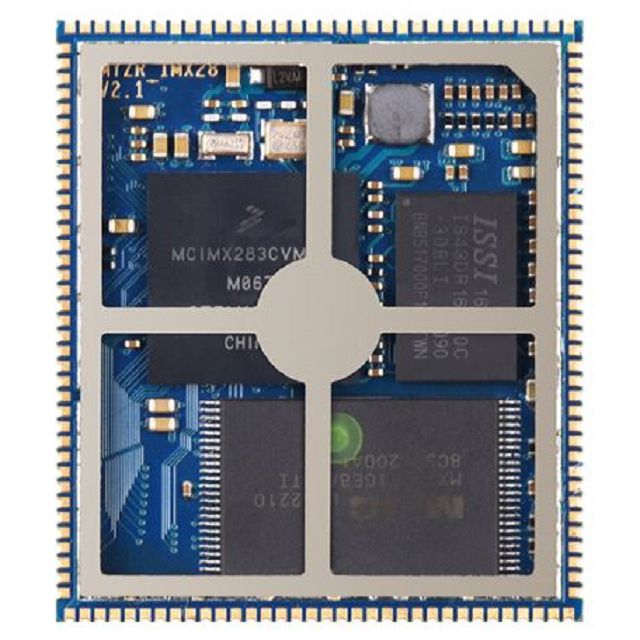

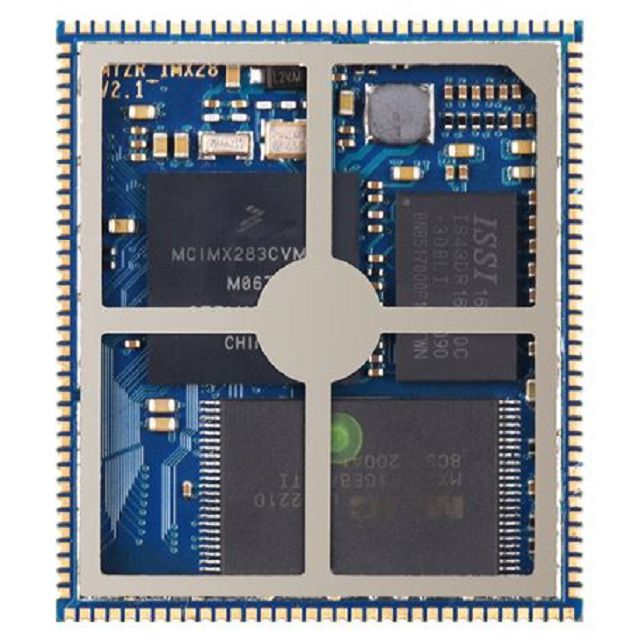

Model: MY-IMX6-CB200-6S5E

CPU:i.MX6S

Memory: DDR3 1GB, up to 2GB

Storage: SPI NorFlash/4GB EMMC, Up to 64 GB EMMC

Power supply: 5V

Size: 40mm x 68mm

Working Temperature:Commercial expansion grade(-20°C..85°C), up to 1.2 GHz

Main Features

4x ARM Cortex-A9 up to 1GHz per core at work

200 Mtri/s 1000Mpxl/s, OpenGL ES 2.0&Halti, CL EP

1MB L2cache

GPU 2D(Vector Graphics)

32KB instruction and data cache

Vivante GC355 300Mpxl/s, Open VG1.1

NEON SIMDmedia accelerator

GPU 2D(Composition)

GPU 3D

Vivante GC320 600Mpxl/s, BLIT

Vivante GC2000

Video Decode:1080p 60h.264

Hardware BCH(up to 20 corrections)

Video Encode:1080p30H. 264BP 2x720p encode

Camera Interface

Types: 1x 20-bit parallel, MIPI-CSI-2(2 lanes), three simultaneous inputs

OS Support

Linux 3.0.35/Linux 3.14.52/Linux-4.1.15, Android4.4.2/Android5.1, QT4.8.5/QT5, Ubuntu12.04/Ubuntu16.04

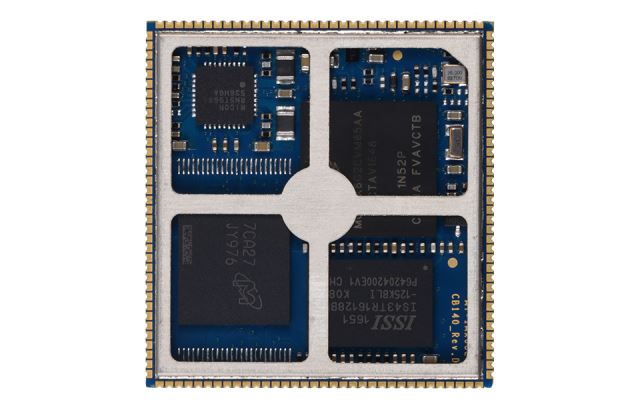

MY-IMX6-CB200 parameter

hardware configuration

core board main model | CPU | memory capacity | storage capacity | boot mode | burning mode | other |

MY-IMX6-CB200 | i.MX 6QP | 1G / 2G | eMMC: 4G ~ 64G | SPI Flash | two bit dialing | standard configuration:memory 1G,storage 4G |

i.MX 6Q | 1G / 2G | eMMC: 4G ~ 64G | SPI Flash | two bit dialing | standard configuration:memory 1G,storage 4G | |

i.MX 6U | 1G | eMMC: 4G ~ 64G | SPI Flash | two bit dialing | standard configuration:memory 1G,storage 4G | |

i.MX 6S | 512M / 1G | eMMC: 4G ~ 64G | SPI Flash | two bit dialing | standard configuration:memory 512M,storage 4G | |

MY-IMX6-CB314 | i.MX 6QP | 1G / 2G | eMMC: 4G ~ 64G | SPI Flash | two bit dialing | standard configuration:memory 1G,storage 4G |

i.MX 6Q | 1G / 2G | eMMC: 4G ~ 64G | SPI Flash | two bit dialing | standard configuration:memory 1G,storage 4G | |

i.MX 6U | 1G | eMMC: 4G ~ 64G | SPI Flash | two bit dialing | standard configuration:memory 1G,storage 4G | |

MY-IMX6-CB336 | i.MX 6QP | 1G / 2G | eMMC: 4G ~ 64G | SPI Flash | two bit dialing | standard configuration:memory 1G,storage 4G |

i.MX 6Q | 1G / 2G | eMMC: 4G ~ 64G | SPI Flash | two bit dialing | standard configuration:memory 1G,storage 4G | |

Instruction:the series of core boards mentioned above can be offered in grades of automotive/industrical control/consumer electronic?standard configuration is consumer electronic?) | ||||||

Operating system support

Operating system & version | MY-IMX6-EK200 | MY-IMX6-EK314 | MY-IMX6-EK336 | MY-IMX6-EK140 | |

Linux | Linux-3.0.35 | YES | YES | - | - |

Linux-3.14.52 | YES | YES | YES | YES | |

Android | Android 4.2.2 | YES | - | - | - |

Android 4.4.2 | YES | YES | - | - | |

QT | QT-4.8.5 | YES | YES | - | YES |

QT-5.5.0 | YES | YES | YES | - | |

Ubuntu | Ubuntu 11.10 | YES | YES | - | - |

Ubuntu 12.04 | YES | YES | - | - | |

Hardware interface

Display module | HDMI | 1 way | 1.4 port |

LVDS | 2 way | 8bit model up to 165 Mpixels/s | |

RGB | 1 way | 24bit model | |

Rowspan=2|camera | CSI | 1 way | 8bit model |

Mipi | 1 way | 2 Lanes | |

Ethernet camera | RMII | 1 way | 100M |

USB to ethernet camera | 1 way | 100M | |

Audio | I2S/SSI/AC97 | 1 way | up to 1.4 Mbps |

PCI Express | PCI Express | 1 way | Gen 2.0 |

Storage | SD/MMC? | 2 way | 4/8bit |

SATA | 1 way | SATA II, 3.0 Gbps | |

USB | USBOTG | 1 way | 480M high speed |

USBHOST | 1 way | 480M high speed | |

CSPI | CSPI | 2 way | high speed |

UART | UART | 5 | up to 4.0 Mbps |

CAN | CAN | 2 way | 1 Mbps each |

PWM | PWM | 1 way | configuration of 4 way is optional |

I2C | I2C | 3 way | supporting 400 kbps |

IO expansion | multiple way | 21 way | other pins can be configured as IO |

Watchdog | watch dog | 1 way | watchdog inside CPU |

Defaulted display selection

LVDS0 LVDS0 7? TFT crystal liquid display(24bit LVDS port)

resolution 1024X600@60Hz

white backlight

capacitor touch

LVDS1

LVDS1 7-inch TFT crystal liquid display(24bit LVDS port)

resolution 1024X600@60Hz

white backlight

capacitor touch

GRB

7-inch TFT crystal liquid display(24bit RGB port)

resolution 800X480@60Hz

white backlight

capacitor touch

HDMI

HDMI-output (24bit HDMI port)

1920X1080@60Hz compatible 16/18/24bpp

Definition of pin

| 1 | GND | POWER | 5V_IN | 2 | |

3 | 4 | ||||

5 | 6 | ||||

7 | 8 | ||||

9 | 10 | ||||

11 | NANDF_CS0 | GPIO | POWER | 3V_OUT | 12 |

13 | NANDF_CS1 | 14 | |||

15 | NANDF_CS2 | 16 | |||

17 | SD1_DAT0 | 18 | |||

19 | SD3_RST | GPIO | GPIO_4 | 20 | |

21 | KEY_COL2 | EIM_BCLK | 22 | ||

23 | EIM_D20 | CSI0_DATA_EN | 24 | ||

25 | CSPI2_CS0 | CSPI2 | UART2 | UART2_CTS | 26 |

27 | CSPI2_RDY | UART2_RTS | 28 | ||

29 | CSPI2_MOSI | UART2_TXD | 30 | ||

31 | CSPI2_CLK | UART2_RXD | 32 | ||

33 | CSPI2_CS1 | UART3 | UART3_CTS | 34 | |

35 | CSPI2_MISO | UART3_RTS | 36 | ||

37 | MX6_ONOFF | ON/OFF | UART3_TXD | 38 | |

39 | nRESET | nRESET IN | UART3_RXD | 40 | |

41 | CSPI1_CS0 | CSPI1 | SD2 | SD2_DATA2 | 42 |

43 | CSPI1_MISO | SD2_DATA0 | 44 | ||

45 | CSPI1_MOSI | SD2_CLK | 46 | ||

47 | CSPI1_CLK | SD2_DATA3 | 48 | ||

49 | CSPI1_RDY | SD2_CMD | 50 | ||

51 | GND | POWER | SD2_DATA1 | 52 | |

53 | SD3_DATA3 | SD3 | SATA | SATA_RXP | 54 |

55 | SD3_DATA2 | SATA_RXN | 56 | ||

57 | SD3_CMD | SATA_TXN | 58 | ||

59 | SD3_CLK | SATA_TXP | 60 | ||

61 | SD3_DATA1 | USBOTG | USB_OTG_OC | 62 | |

63 | SD3_DATA0 | USB_OTG_PWR_EN | 64 | ||

65 | GND | POWER | USB_OTG_DN | 66 | |

67 | USB_H1_PWR_EN | USBHOST | USB_OTG_DP | 68 | |

69 | USB_HOST_DN | USB_OTG_VBUS | 70 | ||

71 | USB_HOST_DP | USB_OTG_ID | 72 | ||

73 | USB_H1_OC | MINI_PCIE | PCIE_RXP | 74 | |

75 | USB_H1_VBUS | PCIE_RXM | 76 | ||

77 | CSI_D1M | MIPI_CSI | PCIE_TXP | 78 | |

79 | CSI_D1P | PCIE_TXM | 80 | ||

81 | CSI_D0M | CLK1_P | 82 | ||

83 | CSI_D0P | CLK1_N | 84 | ||

85 | CSI_CLK0M | HDMI | HDMI_D2P | 86 | |

87 | CSI_CLK0P | HDMI_D2M | 88 | ||

89 | UART1_RX | UART1 | HDMI_CEC_IN | 90 | |

91 | UART1_TX | HDMI_HPD | 92 | ||

93 | GND | POWER | HDMI_D1P | 94 | |

95 | CSI0_DAT17 | CIS | HDMI_D1M | 96 | |

97 | CSI0_DAT16 | HDMI_CLKP | 98 | ||

99 | CSI0_DAT14 | HDMI_CLKM | 100 | ||

101 | CSI0_DAT19 | HDMI_D0P | 102 | ||

103 | CSI0_DAT18 | HDMI_D0M | 104 | ||

105 | CSI0_DAT13 | I2C1 | I2C1_SCL | 106 | |

107 | CSI0_DAT12 | I2C1_SDA | 108 | ||

109 | CSI0_VSYNCH | AUDIO | AUD3_TXC | 110 | |

111 | CSI0_PIXCLK | AUD3_TXD | 112 | ||

113 | CSI0_HSYNCH | AUD3_RXD | 114 | ||

115 | CSI0_DAT15 | AUD3_TXFS | 116 | ||

117 | CAN1_TX | CAN1 | I2C3 | I2C3_SCL | 118 |

119 | CAN1_RX | I2C3_SDA | 120 | ||

121 | UART4_TXD | UART4 | CAN2 | CAN2_TX | 122 |

123 | UART4_RXD | CAN2_RX | 124 | ||

125 | UART5_RXD | UART5 | CLKOUT | GPIO_0_CLKO | 126 |

127 | UART5_TXD | POWER | GND | 128 | |

129 | LVDS0_TX2_P | LVDS0 | LVDS1 | LVDS1_TX1_N | 130 |

131 | LVDS0_TX2_N | LVDS1_TX1_P | 132 | ||

133 | LVDS0_TX0_N | LVDS1_TX0_P | 134 | ||

135 | LVDS0_TX0_P | LVDS1_TX0_N | 136 | ||

137 | LVDS0_TX3_N | LVDS1_TX3_N | 138 | ||

139 | LVDS0_TX3_P | LVDS1_TX3_P | 140 | ||

141 | LVDS0_CLK_N | LVDS1_TX2_P | 142 | ||

143 | LVDS0_CLK_P | LVDS1_TX2_N | 144 | ||

145 | LVDS0_TX1_N | LVDS1_CLK_N | 146 | ||

147 | LVDS0_TX1_P | LVDS1_CLK_P | 148 | ||

149 | GND | POWER | GPIO | NANDF_ALE | 150 |

151 | SD1_DAT1 | GPIO | NANDF_CLE | 152 | |

153 | SD1_DAT2 | NANDF_WP_B | 154 | ||

155 | NANDF_CS3 | SD1_CLK | 156 | ||

157 | DISP0_DAT16 | LCD | I2C2 | I2C2_SCL | 158 |

159 | DISP0_DAT23 | I2C2_SDA | 160 | ||

161 | DISP0_DAT11 | LCD | DISP0_DAT19 | 162 | |

163 | DISP0_DAT15 | DISP0_DAT20 | 164 | ||

165 | DISP0_DAT13 | DISP0_DAT6 | 166 | ||

167 | DISP0_DAT8 | DISP0_DAT21 | 168 | ||

169 | DISP0_DAT3 | DISP0_DAT2 | 170 | ||

171 | DISP0_DAT1 | DISP0_DAT10 | 172 | ||

173 | DISP0_DRDY | DISP0_DAT4 | 174 | ||

175 | DISP0_VSYNCH | POWER | GND | 176 | |

177 | DISP0_CONTRAST | FEC | ENET_REF_CLK | 178 | |

179 | DISP0_CLK | ENET_nINT | 180 | ||

181 | DISP0_DAT18 | ENET_RXD1 | 182 | ||

183 | DISP0_DAT22 | ENET_RX_ER | 184 | ||

185 | DISP0_DAT14 | ENET_nRST | 186 | ||

187 | DISP0_DAT17 | ENET_MDIO | 188 | ||

189 | DISP0_DAT9 | ENET_CRS_DV | 190 | ||

191 | DISP0_DAT12 | ENET_TX_EN | 192 | ||

193 | DISP0_DAT5 |

|

| ENET_TXD1 | 194 |

195 | DISP0_DAT7 | ENET_RXD0 | 196 | ||

197 | DISP0_DAT0 | ENET_MDC | 198 | ||

199 | DISP0_HSYNCH | ENET_TXD0 | 200 | ||

Instruction of detailed function of pins

Form 1

Pin | CPU Ball Name | Pin Name | function selection | module affiliated | function description | voltage |

1 | NC | GND |

| power supply | digitally | 0V |

3 | ||||||

5 | ||||||

7 | ||||||

9 | ||||||

11 | F15 | NANDF_CS0 | 0 | rawnand | CE0N | 3.3V |

3 | usboh3 | UH3_DFD_OUT[15] | ||||

4 | usboh3 | UH2_DFD_OUT[15] | ||||

5 | gpio6 | GPIO[11] | ||||

7 | pl301_mx6q_per1 | HSIZE[2] | ||||

13 | C16 | NANDF_CS1 | 0 | rawnand | CE1N | 3.3V |

1 | usdhc4 | VSELECT | ||||

2 | usdhc3 | VSELECT | ||||

4 | pcie_ctrl | DIAG_STATUS_BUS_MUX[3] | ||||

5 | gpio6 | GPIO[14] | ||||

7 | pl301_mx6q_per1 | HREADYOUT | ||||

15 | A17 | NANDF_CS2 | 0 | rawnand | CE2N | 3.3V |

1 | ipu1 | SISG[0] | ||||

2 | esai1 | TX0 | ||||

3 | weim | WEIM_CRE | ||||

4 | ccm | CLKO2 | ||||

5 | gpio6 | GPIO[15] | ||||

6 | ipu2 | SISG[0] | ||||

17 | A21 | SD1_DAT0 | 0 | usdhc1 | DAT0 | 3.3V |

1 | ecspi5 | MISO | ||||

2 | caam_wrapper | RNG_OSC_OBS | ||||

3 | gpt | CAPIN1 | ||||

4 | pcie_ctrl | DIAG_STATUS_BUS_MUX[8] | ||||

5 | gpio1 | GPIO[16] | ||||

6 | hdmi_tx | OPHYDTB[1] | ||||

19 | D15 | SD3_RST | 0 | usdhc3 | RST | 3.3V |

1 | uart3 | RTS | ||||

2 | pcie_ctrl | DIAG_STATUS_BUS_MUX[30] | ||||

3 | usboh3 | UH3_DFD_OUT[10] | ||||

4 | usboh3 | UH2_DFD_OUT[10] | ||||

5 | gpio7 | GPIO[8] | ||||

6 | mipi_core | DPHY_TEST_IN[22] | ||||

21 | W6 | KEY_COL2 | 2 | can1 | TXCAN | |

3 | kpp | COL[2] | ||||

4 | enet | MDC | ||||

5 | gpio4 | GPIO[10] | ||||

6 | usboh3 | H1USB_PWRCTL_WAKEUP | ||||

7 | pl301_mx6q_per1 | HADDR[3] | ||||

23 | G20 | EIM_D20 | 0 | weim | WEIM_D[20] | 3.3V |

1 | ecspi4 | SS0 | ||||

2 | ipu1 | DI0_PIN16 | ||||

3 | ipu2 | CSI1_D[15] | ||||

4 | uart1 | RTS | ||||

5 | gpio3 | GPIO[20] | ||||

6 | epit2 | EPITO | ||||

25 | K20 | CSPI2_CS0 | 0 | weim | WEIM_RW | 3.3V |

1 | ipu1 | DI1_PIN8 | ||||

2 | ecspi2 | SS0 | ||||

4 | mipi_core | DPHY_TEST_OUT[27] | ||||

5 | gpio2 | GPIO[26] | ||||

6 | tpsmp | HDATA[10] | ||||

7 | src | BT_CFG[29] | ||||

27 | H19 | CSPI2_RDY | 0 | weim | WEIM_A[25] | 3.3V |

1 | ecspi4 | SS1 | ||||

2 | ecspi2 | RDY | ||||

3 | ipu1 | DI1_PIN12 | ||||

4 | ipu1 | DI0_D1_CS | ||||

5 | gpio5 | GPIO[2] | ||||

6 | hdmi_tx | CEC_LINE | ||||

7 | pl301_mx6q_per1 | HBURST[0] | ||||

29 | J23 | CSPI2_MOSI | 0 | weim | WEIM_CS[1] | 3.3V |

1 | ipu1 | DI1_PIN6 | ||||

2 | ecspi2 | MOSI | ||||

4 | mipi_core | DPHY_TEST_OUT[25] | ||||

5 | gpio2 | GPIO[24] | ||||

6 | tpsmp | HDATA[8] | ||||

31 | H24 | CSPI2_CLK | 0 | weim | WEIM_CS[0] | 3.3V |

1 | ipu1 | DI1_PIN5 | ||||

2 | ecspi2 | SCLK | ||||

4 | mipi_core | DPHY_TEST_OUT[24] | ||||

5 | gpio2 | GPIO[23] | ||||

6 | tpsmp | HDATA[7] | ||||

33 | K22 | CSPI2_CS1 | 0 | weim | WEIM_LBA | 3.3V |

1 | ipu1 | DI1_PIN17 | ||||

2 | ecspi2 | SS1 | ||||

5 | gpio2 | GPIO[27] | ||||

6 | tpsmp | HDATA[11] | ||||

7 | src | BT_CFG[26] | ||||

35 | J24 | CSPI2_MISO | 0 | weim | WEIM_OE | 3.3V |

1 | ipu1 | DI1_PIN7 | ||||

2 | ecspi2 | MISO | ||||

4 | mipi_core | DPHY_TEST_OUT[26] | ||||

5 | gpio2 | GPIO[25] | ||||

6 | tpsmp | HDATA[9] | ||||

37 | D12 | MX6_ONOFF |

| MX6_ONOFF | ON/OFF | 3.3V |

39 | NC | nRESET |

| nRESET | nRESET | 3.3V |

41 | E22 | CSPI1_CS0 | 0 | weim | WEIM_EB[2] | 3.3V |

1 | ecspi1 | SS0 | ||||

2 | ccm | DI1_EXT_CLK | ||||

3 | ipu2 | CSI1_D[19] | ||||

4 | hdmi_tx | DDC_SCL | ||||

5 | gpio2 | GPIO[30] | ||||

6 | i2c2 | SCL | ||||

7 | src | BT_CFG[30] | ||||

43 | F21 | CSPI1_MISO | 0 | weim | WEIM_D[17] | 3.3V |

1 | ecspi1 | MISO | ||||

2 | ipu1 | DI0_PIN6 | ||||

3 | ipu2 | CSI1_PIXCLK | ||||

4 | dcic1 | DCIC_OUT | ||||

5 | gpio3 | GPIO[17] | ||||

6 | i2c3 | SCL | ||||

7 | pl301_mx6q_per1 | HBURST[1] | ||||

45 | D24 | CSPI1_MOSI | 0 | weim | WEIM_D[18] | 3.3V |

1 | ecspi1 | MOSI | ||||

2 | ipu1 | DI0_PIN7 | ||||

3 | ipu2 | CSI1_D[17] | ||||

4 | ipu1 | DI1_D0_CS | ||||

5 | gpio3 | GPIO[18] | ||||

6 | i2c3 | SDA | ||||

7 | pl301_mx6q_per1 | HBURST[2] | ||||

47 | C25 | CSPI1_CLK | 0 | weim | WEIM_D[16] | 3.3V |

1 | ecspi1 | SCLK | ||||

2 | ipu1 | DI0_PIN5 | ||||

3 | ipu2 | CSI1_D[18] | ||||

4 | hdmi_tx | DDC_SDA | ||||

5 | gpio3 | GPIO[16] | ||||

6 | i2c2 | SDA | ||||

49 | P5 | CSPI1_RDY | 0 | kpp | COL[5] | 3.3V |

1 | enet | 1588_EVENT0_OUT | ||||

2 | spdif | OUT1 | ||||

3 | ccm | CLKO | ||||

4 | ecspi1 | RDY | ||||

5 | gpio4 | GPIO[5] | ||||

6 | enet | TX_ER | ||||

7 | src | INT_BOOT | ||||

51 | NC | GND |

|

|

| 0V |

53 | B15 | SD3_DATA3 | 0 | usdhc3 | DAT3 | 3.3V |

1 | uart3 | CTS | ||||

2 | pcie_ctrl | DIAG_STATUS_BUS_MUX[29] | ||||

3 | usboh3 | UH3_DFD_OUT[9] | ||||

4 | usboh3 | UH2_DFD_OUT[9] | ||||

5 | gpio7 | GPIO[7] | ||||

6 | mipi_core | DPHY_TEST_IN[21] | ||||

55 | A15 | SD3_DATA2 | 0 | usdhc3 | DAT2 | 3.3V |

2 | pcie_ctrl | DIAG_STATUS_BUS_MUX[28] | ||||

3 | usboh3 | UH3_DFD_OUT[8] | ||||

4 | usboh3 | UH2_DFD_OUT[8] | ||||

5 | gpio7 | GPIO[6] | ||||

6 | mipi_core | DPHY_TEST_IN[20] | ||||

57 | B13 | SD3_CMD | 0 | usdhc3 | CMD | 3.3V |

1 | uart2 | CTS | ||||

2 | can1 | TXCAN | ||||

3 | usboh3 | UH3_DFD_OUT[4] | ||||

4 | usboh3 | UH2_DFD_OUT[4] | ||||

5 | gpio7 | GPIO[2] | ||||

6 | mipi_core | DPHY_TEST_IN[16] | ||||

59 | D14 | SD3_CLK | 0 | usdhc3 | CLK | 3.3V |

1 | uart2 | RTS | ||||

2 | can1 | RXCAN | ||||

3 | usboh3 | UH3_DFD_OUT[5] | ||||

4 | usboh3 | UH2_DFD_OUT[5] | ||||

5 | gpio7 | GPIO[3] | ||||

6 | mipi_core | DPHY_TEST_IN[17] | ||||

61 | F14 | SD3_DATA1 | 0 | usdhc3 | DAT1 | 3.3V |

1 | uart1 | RTS | ||||

2 | can2 | RXCAN | ||||

3 | usboh3 | UH3_DFD_OUT[7] | ||||

4 | usboh3 | UH2_DFD_OUT[7] | ||||

5 | gpio7 | GPIO[5] | ||||

6 | mipi_core | DPHY_TEST_IN[19] | ||||

63 | E14 | SD3_DATA0 | 0 | usdhc3 | DAT0 | 3.3V |

1 | uart1 | CTS | ||||

2 | can2 | TXCAN | ||||

3 | usboh3 | UH3_DFD_OUT[6] | ||||

4 | usboh3 | UH2_DFD_OUT[6] | ||||

5 | gpio7 | GPIO[4] | ||||

6 | mipi_core | DPHY_TEST_IN[18] | ||||

65 | NC | GND |

|

|

| 0V |

67 | C13 | USB_H1_PWR_EN | 0 | usdhc3 | DAT5 | 3.3V |

1 | uart2 | TXD_MUX | ||||

2 | pcie_ctrl | DIAG_STATUS_BUS_MUX[26] | ||||

3 | usboh3 | UH3_DFD_OUT[2] | ||||

4 | usboh3 | UH2_DFD_OUT[2] | ||||

5 | gpio7 | GPIO[0] | ||||

6 | mipi_core | DPHY_TEST_IN[14] | ||||

69 | F10 | USB_HOST_DN |

| USBHOST | USB_HOST_DN | 2.5V |

71 | E10 | USB_HOST_DP |

| USBHOST | USB_HOST_DP | 2.5V |

73 | J20 | USB_H1_OC | 0 | weim | WEIM_D[30] | 3.3V |

1 | ipu1 | DISP1_DAT[21] | ||||

2 | ipu1 | DI0_PIN11 | ||||

3 | ipu1 | CSI0_D[3] | ||||

4 | uart3 | CTS | ||||

5 | gpio3 | GPIO[30] | ||||

6 | usboh3 | USBH1_OC | ||||

7 | pl301_mx6q_per1 | HPROT[0] | ||||

75 | D10 | USB_H1_VBUS |

|

| USB_H1_VBUS | 5V |

77 | D1 | CSI_D1M |

| CSI_MIPI | CSI_D1M | 2.5V |

79 | D2 | CSI_D1P |

| CSI_D1P | ||

81 | E4 | CSI_D0M |

| CSI_D0M | ||

83 | E3 | CSI_D0P |

| CSI_D0P | ||

85 | F4 | CSI_CLK0M |

| CSI_CLK0M | ||

87 | F3 | CSI_CLK0P |

| CSI_CLK0P | ||

89 | M3 | UART1_RX | 0 | ipu1 | CSI0_D[11] | 2.5V |

1 | audmux | AUD3_RXFS | ||||

2 | ecspi2 | SS0 | ||||

3 | uart1 | RXD_MUX | ||||

4 | sdma | DEBUG_PC[5] | ||||

5 | gpio5 | GPIO[29] | ||||

6 | mmdc | MMDC_DEBUG[34] | ||||

7 | ARMCortexA9 MPCorePlatform | TRACE[8] | ||||

91 | M1 | UART1_TX | 0 | ipu1 | CSI0_D[10] | 2.5V |

1 | audmux | AUD3_RXC | ||||

2 | ecspi2 | MISO | ||||

3 | uart1 | TXD_MUX | ||||

4 | sdma | DEBUG_PC[4] | ||||

5 | gpio5 | GPIO[28] | ||||

6 | mmdc | MMDC_DEBUG[33] | ||||

7 | ARMCortexA9 MPCorePlatform | TRACE[7] | ||||

93 | NC | GND |

|

|

| 0V |

95 | L3 | CSI0_DAT17 | 0 | ipu1 | CSI0_D[17] | 2.5V |

1 | weim | WEIM_D[13] | ||||

2 | pcie_ctrl | DIAG_STATUS_BUS_MUX[21] | ||||

3 | uart4 | CTS | ||||

4 | sdma | DEBUG_PC[11] | ||||

5 | gpio6 | GPIO[3] | ||||

6 | mmdc | MMDC_DEBUG[40] | ||||

7 | ARMCortexA9 MPCorePlatform | TRACE[14] | ||||

97 | L4 | CSI0_DAT16 | 0 | ipu1 | CSI0_D[16] | 2.5V |

1 | weim | WEIM_D[12] | ||||

2 | pcie_ctrl | DIAG_STATUS_BUS_MUX[20] | ||||

3 | uart4 | RTS | ||||

4 | sdma | DEBUG_PC[10] | ||||

5 | gpio6 | GPIO[2] | ||||

6 | mmdc | MMDC_DEBUG[39] | ||||

7 | ARMCortexA9 MPCorePlatform | TRACE[13] | ||||

99 | M4 | CSI0_DAT14 | 0 | ipu1 | CSI0_D[14] | 2.5V |

1 | weim | WEIM_D[10] | ||||

2 | pcie_ctrl | DIAG_STATUS_BUS_MUX[18] | ||||

3 | uart5 | TXD_MUX | ||||

4 | sdma | DEBUG_PC[8] | ||||

5 | gpio6 | GPIO[0] | ||||

6 | mmdc | MMDC_DEBUG[37] | ||||

7 | ARMCortexA9 MPCorePlatform | TRACE[11] | ||||

101 | L6 | CSI0_DAT19 | 0 | ipu1 | CSI0_D[19] | 2.5V |

1 | weim | WEIM_D[15] | ||||

2 | pcie_ctrl | DIAG_STATUS_BUS_MUX[23] | ||||

3 | uart5 | CTS | ||||

4 | sdma | DEBUG_PC[13] | ||||

5 | gpio6 | GPIO[5] | ||||

6 | mmdc | MMDC_DEBUG[42] | ||||

103 | M6 | CSI0_DAT18 | 0 | ipu1 | CSI0_D[18] | 2.5V |

1 | weim | WEIM_D[14] | ||||

2 | pcie_ctrl | DIAG_STATUS_BUS_MUX[22] | ||||

3 | uart5 | RTS | ||||

4 | sdma | DEBUG_PC[12] | ||||

5 | gpio6 | GPIO[4] | ||||

6 | mmdc | MMDC_DEBUG[41] | ||||

7 | ARMCortexA9 MPCorePlatform | TRACE[15] | ||||

105 | L1 | CSI0_DAT13 | 0 | ipu1 | CSI0_D[13] | 2.5V |

1 | weim | WEIM_D[9] | ||||

2 | pcie_ctrl | DIAG_STATUS_BUS_MUX[17] | ||||

3 | uart4 | RXD_MUX | ||||

4 | sdma | DEBUG_PC[7] | ||||

5 | gpio5 | GPIO[31] | ||||

6 | mmdc | MMDC_DEBUG[36] | ||||

7 | ARMCortexA9 MPCorePlatform | TRACE[10] | ||||

107 | M2 | CSI0_DAT12 | 0 | ipu1 | CSI0_D[12] | 2.5V |

1 | weim | WEIM_D[8] | ||||

2 | pcie_ctrl | DIAG_STATUS_BUS_MUX[16] | ||||

3 | uart4 | TXD_MUX | ||||

4 | sdma | DEBUG_PC[6] | ||||

5 | gpio5 | GPIO[30] | ||||

6 | mmdc | MMDC_DEBUG[35] | ||||

7 | ARMCortexA9 MPCorePlatform | TRACE[9] | ||||

109 | N2 | CSI0_VSYNCH | 0 | ipu1 | CSI0_VSYNC | 2.5V |

1 | weim | WEIM_D[1] | ||||

2 | pcie_ctrl | DIAG_STATUS_BUS_MUX[15] | ||||

4 | sdma | DEBUG_PC[3] | ||||

5 | gpio5 | GPIO[21] | ||||

6 | mmdc | MMDC_DEBUG[32] | ||||

7 | ARMCortexA9 MPCorePlatform | TRACE[0] | ||||

111 | P1 | CSI0_PIXCLK | 0 | ipu1 | CSI0_PIXCLK | 2.5V |

2 | pcie_ctrl | DIAG_STATUS_BUS_MUX[12] | ||||

4 | sdma | DEBUG_PC[0] | ||||

5 | gpio5 | GPIO[18] | ||||

6 | mmdc | MMDC_DEBUG[29] | ||||

7 | ARMCortexA9 MPCorePlatform | EVENTO | ||||

113 | P4 | CSI0_HSYNCH | 0 | ipu1 | CSI0_HSYNC | 2.5V |

2 | pcie_ctrl | DIAG_STATUS_BUS_MUX[13] | ||||

3 | ccm | CLKO | ||||

4 | sdma | DEBUG_PC[1] | ||||

5 | gpio5 | GPIO[19] | ||||

6 | mmdc | MMDC_DEBUG[30] | ||||

7 | ARMCortexA9 MPCorePlatform | TRCTL | ||||

115 | M5 | CSI0_DAT15 | 0 | ipu1 | CSI0_D[15] | 2.5V |

1 | weim | WEIM_D[11] | ||||

2 | pcie_ctrl | DIAG_STATUS_BUS_MUX[19] | ||||

3 | uart5 | RXD_MUX | ||||

4 | sdma | DEBUG_PC[9] | ||||

5 | gpio6 | GPIO[1] | ||||

6 | mmdc | MMDC_DEBUG[38] | ||||

7 | ARMCortexA9 MPCorePlatform | TRACE[12] | ||||

117 | R3 | CAN1_TX | 0 | esai1 | TX4_RX1 | 3.3V |

1 | ecspi5 | RDY | ||||

2 | epit1 | EPITO | ||||

3 | can1 | TXCAN | ||||

4 | uart2 | TXD_MUX | ||||

5 | gpio1 | GPIO[7] | ||||

6 | spdif | PLOCK | ||||

7 | usboh3 | OTGUSB_HOST_MODE | ||||

119 | R5 | CAN1_RX | 0 | esai1 | TX5_RX0 | 3.3V |

2 | epit2 | EPITO | ||||

3 | can1 | RXCAN | ||||

4 | uart2 | RXD_MUX | ||||

5 | gpio1 | RXD_MUX | ||||

6 | spdif | SRCLK | ||||

7 | usboh3 |

| ||||

121 | W5 | UART4_TXD | 0 | ecspi1 | SCLK | 3.3V |

1 | enet | RDATA[3] | ||||

2 | audmux | AUD5_TXC | ||||

3 | kpp | COL[0] | ||||

4 | uart4 | TXD_MUX | ||||

5 | gpio4 | GPIO[6] | ||||

6 | dcic1 | DCIC_OUT | ||||

7 | src | ANY_PU_RST | ||||

123 | V6 | UART4_RXD | 0 | ecspi1 | MOSI | 3.3V |

1 | enet | TDATA[3] | ||||

2 | audmux | AUD5_TXD | ||||

3 | kpp | ROW[0] | ||||

4 | uart4 | RXD_MUX | ||||

5 | gpio4 | GPIO[7] | ||||

6 | dcic2 | DCIC_OUT | ||||

7 | pl301_mx6q_per1 | HADDR[0] | ||||

125 | U6 | UART5_RXD | 0 | ecspi1 | SS0 | 3.3V |

1 | enet | COL | ||||

2 | audmux | AUD5_RXD | ||||

3 | kpp | ROW[1] | ||||

4 | uart5 | RXD_MUX | ||||

5 | gpio4 | GPIO[9] | ||||

6 | usdhc2 | VSELECT | ||||

7 | pl301_mx6q_per1 | HADDR[2] | ||||

127 | U7 | UART5_TXD | 0 | ecspi1 | MISO | 3.3V |

1 | enet | MDIO | ||||

2 | audmux | AUD5_TXFS | ||||

3 | kpp | COL[1] | ||||

4 | uart5 | TXD_MUX | ||||

5 | gpio4 | GPIO[8] | ||||

6 | usdhc1 | VSELECT | ||||

7 | pl301_mx6q_per1 | HADDR[1] | ||||

129 | V1 | LVDS0_TX2_P |

| LVDS0 | LVDS0_TX2_P | 2.5V |

131 | V2 | LVDS0_TX2_N |

| LVDS0_TX2_N | ||

133 | U2 | LVDS0_TX0_N |

| LVDS0_TX0_N | ||

135 | U1 | LVDS0_TX0_P |

| LVDS0_TX0_P | ||

137 | W2 | LVDS0_TX3_N |

| LVDS0_TX3_N | ||

139 | W1 | LVDS0_TX3_P |

| LVDS0_TX3_P | ||

141 | V4 | LVDS0_CLK_N |

| LVDS0_CLK_N | ||

143 | V3 | LVDS0_CLK_P |

| LVDS0_CLK_P | ||

145 | U4 | LVDS0_TX1_N |

| LVDS0_TX1_N | ||

147 | U3 | LVDS0_TX1_P |

| LVDS0_TX1_P | ||

149 | NC | GND |

|

|

| 0V |

151 | C20 | SD1_DAT1 | 0 | usdhc1 | DAT1 | 3.3V |

1 | ecspi5 | SS0 | ||||

2 | pwm3 | PWMO | ||||

3 | gpt | CAPIN2 | ||||

4 | pcie_ctrl | DIAG_STATUS_BUS_MUX[7] | ||||

5 | gpio1 | GPIO[17] | ||||

6 | hdmi_tx | OPHYDTB[0] | ||||

153 | E19 | SD1_DAT2 | 0 | usdhc1 | DAT2 | 3.3V |

1 | ecspi5 | SS1 | ||||

2 | gpt | CMPOUT2 | ||||

3 | pwm2 | PWMO | ||||

4 | wdog1 | WDOG_B | ||||

5 | gpio1 | GPIO[19] | ||||

6 | wdog1 | WDOG_RST_B_DEB | ||||

155 | D16 | NANDF_CS3 | 0 | rawnand | CE3N | 3.3V |

1 | ipu1 | SISG[1] | ||||

2 | esai1 | TX1 | ||||

3 | weim | WEIM_A[26] | ||||

4 | pcie_ctrl | DIAG_STATUS_BUS_MUX[4] | ||||

5 | gpio6 | GPIO[16] | ||||

6 | ipu2 | SISG[1] | ||||

7 | tpsmp | CLK | ||||

157 | T21 | DISP0_DAT16 | 0 | ipu1 | DISP0_DAT[16] | 3.3V |

1 | ipu2 | DISP0_DAT[16] | ||||

2 | ecspi2 | MOSI | ||||

3 | audmux | AUD5_TXC | ||||

4 | sdma | SDMA_EXT_EVENT[0] | ||||

5 | gpio5 | GPIO[10] | ||||

6 | mmdc | MMDC_DEBUG[21] | ||||

7 | pl301_mx6q_per1 | HADDR[26] | ||||

159 | W24 | DISP0_DAT23 | 0 | ipu1 | DISP0_DAT[23] | 3.3V |

1 | ipu2 | DISP0_DAT[23] | ||||

2 | ecspi1 | SS0 | ||||

3 | audmux | AUD4_RXD | ||||

4 | sdma | DEBUG_BUS_DEVICE[2] | ||||

5 | gpio5 | GPIO[17] | ||||

6 | mmdc | MMDC_DEBUG[28] | ||||

7 | pl301_mx6q_per1 | HADDR[31] | ||||

161 | T23 | DISP0_DAT11 | 0 | ipu1 | DISP0_DAT[11] | 3.3V |

1 | ipu2 | DISP0_DAT[11] | ||||

3 | usdhc1 | USDHC_DEBUG[7] | ||||

4 | sdma | DEBUG_EVENT_CHANNEL[4] | ||||

5 | gpio5 | GPIO[5] | ||||

6 | mmdc | MMDC_DEBUG[16] | ||||

7 | pl301_mx6q_per1 | HADDR[22] | ||||

163 | T22 | DISP0_DAT15 | 0 | ipu1 | DISP0_DAT[15] | 3.3V |

1 | ipu2 | DISP0_DAT[15] | ||||

2 | ecspi1 | SS1 | ||||

3 | ecspi2 | SS1 | ||||

4 | sdma | DEBUG_EVT_CHN_LINES[2] | ||||

5 | gpio5 | GPIO[9] | ||||

6 | mmdc | MMDC_DEBUG[20] | ||||

7 | pl301_mx6q_per1 | HADDR[25] | ||||

165 | R20 | DISP0_DAT13 | 0 | ipu1 | DISP0_DAT[13] | 3.3V |

1 | ipu2 | DISP0_DAT[13] | ||||

3 | audmux | AUD5_RXFS | ||||

4 | sdma | DEBUG_EVT_CHN_LINES[0] | ||||

5 | gpio5 | GPIO[7] | ||||

6 | mmdc | MMDC_DEBUG[18] | ||||

7 | pl301_mx6q_per1 | HADDR[24] | ||||

167 | R22 | DISP0_DAT8 | 0 | ipu1 | DISP0_DAT[8] | 3.3V |

1 | ipu2 | DISP0_DAT[8] | ||||

2 | pwm1 | PWMO | ||||

3 | wdog1 | WDOG_B | ||||

4 | sdma | DEBUG_EVENT_CHANNEL[1] | ||||

5 | gpio4 | GPIO[29] | ||||

6 | mmdc | MMDC_DEBUG[13] | ||||

7 | pl301_mx6q_per1 | HADDR[19] | ||||

169 | P21 | DISP0_DAT3 | 0 | ipu1 | DISP0_DAT[3] | 3.3V |

1 | ipu2 | DISP0_DAT[3] | ||||

2 | ecspi3 | SS0 | ||||

3 | usdhc1 | USDHC_DEBUG[3] | ||||

4 | sdma | DEBUG_BUS_ERROR | ||||

5 | gpio4 | GPIO[24] | ||||

6 | mmdc | MMDC_DEBUG[8] | ||||

7 | pl301_mx6q_per1 | HADDR[14] | ||||

171 | P22 | DISP0_DAT1 | 0 | ipu1 | DISP0_DAT[1] | 3.3V |

1 | ipu2 | DISP0_DAT[1] | ||||

2 | ecspi3 | MOSI | ||||

3 | usdhc1 | USDHC_DEBUG[1] | ||||

4 | sdma | DEBUG_EVENT_CHANNEL_SEL | ||||

5 | gpio4 | GPIO[22] | ||||

6 | mmdc | MMDC_DEBUG[6] | ||||

7 | pl301_mx6q_per1 | HADDR[12] | ||||

173 | N21 | DISP0_DRDY | 0 | ipu1 | DI0_PIN15 | 3.3V |

1 | ipu2 | DI0_PIN15 | ||||

2 | audmux | AUD6_TXC | ||||

3 | mipi_core | DPHY_TEST_OUT[29] | ||||

4 | sdma | DEBUG_CORE_STATE[1] | ||||

5 | gpio4 | GPIO[17] | ||||

6 | mmdc | MMDC_DEBUG[1] | ||||

175 | N20 | DISP0_VSYNCH | 0 | ipu1 | DI0_PIN3 | 3.3V |

1 | ipu2 | DI0_PIN3 | ||||

2 | audmux | AUD6_TXFS | ||||

3 | mipi_core | DPHY_TEST_OUT[31] | ||||

4 | sdma | DEBUG_CORE_STATE[3] | ||||

5 | gpio4 | GPIO[19] | ||||

6 | mmdc | MMDC_DEBUG[3] | ||||

7 | pl301_mx6q_per1 | HADDR[10] | ||||

177 | F18 | DISP0_CONTRAST | 0 | usdhc1 | DAT3 | 3.3V |

1 | ecspi5 | SS2 | ||||

2 | gpt | CMPOUT3 | ||||

3 | pwm1 | PWMO | ||||

4 | wdog2 | WDOG_B | ||||

5 | gpio1 | GPIO[21] | ||||

6 | wdog2 | WDOG_RST_B_DEB | ||||

179 | N19 | DISP0_CLK | 0 | ipu1 | DI0_DISP_CLK | 3.3V |

1 | ipu2 | DI0_DISP_CLK | ||||

3 | mipi_core | DPHY_TEST_OUT[28] | ||||

4 | sdma | DPHY_TEST_OUT[28] | ||||

5 | gpio4 | GPIO[16] | ||||

6 | mmdc | MMDC_DEBUG[0] | ||||

181 | V25 | DISP0_DAT18 | 0 | ipu1 | DISP0_DAT[18] | 3.3V |

1 | ipu2 | DISP0_DAT[18] | ||||

2 | ecspi2 | SS0 | ||||

3 | audmux | AUD5_TXFS | ||||

4 | audmux | AUD4_RXFS | ||||

5 | gpio5 | GPIO[12] | ||||

6 | mmdc | MMDC_DEBUG[23] | ||||

7 | weim | WEIM_CS[2] | ||||

183 | V24 | DISP0_DAT22 | 0 | ipu1 | DISP0_DAT[22] | 3.3V |

1 | ipu2 | DISP0_DAT[22] | ||||

2 | ecspi1 | MISO | ||||

3 | audmux | AUD4_TXFS | ||||

4 | sdma | DEBUG_BUS_DEVICE[1] | ||||

5 | gpio5 | GPIO[16] | ||||

6 | mmdc | MMDC_DEBUG[27] | ||||

7 | pl301_mx6q_per1 | HADDR[30] | ||||

185 | U25 | DISP0_DAT14 | 0 | ipu1 | DISP0_DAT[14] | 3.3V |

1 | ipu2 | DISP0_DAT[14] | ||||

3 | audmux | AUD5_RXC | ||||

4 | sdma | DEBUG_EVT_CHN_LINES[1] | ||||

5 | gpio5 | GPIO[8] | ||||

6 | mmdc | MMDC_DEBUG[19] | ||||

187 | U24 | DISP0_DAT17 | 0 | ipu1 | DISP0_DAT[17] | 3.3V |

1 | ipu2 | DISP0_DAT[17] | ||||

2 | ecspi2 | DISP0_DAT[17] | ||||

3 | audmux | AUD5_TXD | ||||

4 | sdma | SDMA_EXT_EVENT[1] | ||||

5 | gpio5 | GPIO[11] | ||||

6 | mmdc | MMDC_DEBUG[22] | ||||

7 | pl301_mx6q_per1 | HADDR[27] | ||||

189 | T25 | DISP0_DAT9 | 0 | ipu1 | DISP0_DAT[9] | 3.3V |

1 | ipu2 | DISP0_DAT[9] | ||||

2 | pwm2 | PWMO | ||||

3 | wdog2 | WDOG_B | ||||

4 | sdma | DEBUG_EVENT_CHANNEL[2] | ||||

5 | gpio4 | GPIO[30] | ||||

6 | mmdc | MMDC_DEBUG[14] | ||||

7 | pl301_mx6q_per1 | HADDR[20] | ||||

191 | T24 | DISP0_DAT12 | 0 | ipu1 | DISP0_DAT[12] | 3.3V |

1 | ipu2 | DISP0_DAT[12] | ||||

4 | sdma | DEBUG_EVENT_CHANNEL[5] | ||||

5 | gpio5 | GPIO[6] | ||||

6 | mmdc | MMDC_DEBUG[17] | ||||

7 | pl301_mx6q_per1 | HADDR[23] | ||||

193 | R25 | DISP0_DAT5 | 0 | ipu1 | DISP0_DAT[5] | 3.3V |

1 | ipu2 | DISP0_DAT[5] | ||||

2 | ecspi3 | SS2 | ||||

3 | audmux | AUD6_RXFS | ||||

4 | sdma | DEBUG_MATCHED_DMBUB | ||||

5 | gpio4 | GPIO[26] | ||||

6 | mmdc | MMDC_DEBUG[10] | ||||

7 | pl301_mx6q_per1 | HADDR[16] | ||||

195 | R24 | DISP0_DAT7 | 0 | ipu1 | DISP0_DAT[7] | 3.3V |

1 | ipu2 | DISP0_DAT[7] | ||||

2 | ecspi3 | RDY | ||||

3 | usdhc1 | USDHC_DEBUG[5] | ||||

4 | sdma | DEBUG_EVENT_CHANNE L[0] | ||||

5 | gpio4 | GPIO[28] | ||||

6 | mmdc | MMDC_DEBUG[12] | ||||

7 | pl301_mx6q_per1 | HADDR[18] | ||||

197 | P24 | DISP0_DAT0 | 0 | ipu1 | DISP0_DAT[0] | 3.3V |

1 | ipu2 | DISP0_DAT[0] | ||||

2 | ecspi3 | SCLK | ||||

3 | usdhc1 | USDHC_DEBUG[0] | ||||

4 | sdma | DEBUG_CORE_RUN | ||||

5 | gpio4 | GPIO[21] | ||||

6 | mmdc | MMDC_DEBUG[5] | ||||

199 | N25 | DISP0_HSYNCH | 0 | ipu1 | DI0_PIN2 | 3.3V |

1 | ipu2 | DI0_PIN2 | ||||

2 | audmux | AUD6_TXD | ||||

3 | mipi_core | DPHY_TEST_OUT[30] | ||||

4 | sdma | DEBUG_CORE_STATE[2] | ||||

5 | gpio4 | GPIO[18] | ||||

6 | mmdc | MMDC_DEBUG[2] | ||||

7 | pl301_mx6q_per1 | HADDR[9] |

Form 2

Pin | CPU Ball Name | Pin Name | function selection | module affiliated | function description | voltage | |

2 | NC | 5VIN |

| power supply | 5V input | 5V | |

4 | |||||||

6 | |||||||

8 | |||||||

10 | |||||||

12 | NC | 3P3V |

| power supply | output(1A) | 3.3V | |

14 | |||||||

16 | |||||||

18 | |||||||

20 | R6 | GPIO_4 | 0 | esai1 | HCKT | 3.3V | |

1 | observe_mux | OBSRV_INT_OUT3 | |||||

2 | kpp | COL[7] | |||||

3 | ccm | CCM_OUT_2 | |||||

4 | csu | CSU_ALARM_AUT[1] | |||||

5 | gpio1 | GPIO[4] | |||||

6 | usdhc2 | CD | |||||

7 | ocotp_ctrl_wrapper | FUSE_LATCHED | |||||

22 | N22 | EIM_BCLK | 0 | weim | WEIM_BCLK | 3.3V | |

1 | ipu1 | DI1_PIN16 | |||||

5 | gpio6 | GPIO[31] | |||||

6 | tpsmp | HDATA[31] | |||||

24 | P3 | CSI0_DATA_EN | 0 | ipu1 | CSI0_DATA_EN | 2.5V | |

1 | weim | WEIM_D[0] | |||||

2 | pcie_ctrl | DIAG_STATUS_BUS_MUX[14] | |||||

4 | sdma | DEBUG_PC[2] | |||||

5 | gpio5 | GPIO[20] | |||||

6 | mmdc | MMDC_DEBUG[31] | |||||

7 | ARM CortexA9 MPCore Platform | TRCLK | |||||

26 | G23 | UART2_CTS | 0 | weim | WEIM_D[28] | 3.3V | |

1 | i2c1 | SDA | |||||

2 | ecspi4 | MOSI | |||||

3 | ipu2 | CSI1_D[12] | |||||

4 | uart2 | CTS | |||||

5 | gpio3 | GPIO[28] | |||||

6 | ipu1 | EXT_TRIG | |||||

7 | ipu1 | DI0_PIN13 | |||||

28 | J19 | UART2_RTS | 0 | weim | WEIM_D[29] | 3.3V | |

1 | ipu1 | DI1_PIN15 | |||||

2 | ecspi4 | SS0 | |||||

4 | uart2 | RTS | |||||

5 | gpio3 | GPIO[29] | |||||

6 | ipu2 | CSI1_VSYNC | |||||

7 | ipu1 | DI0_PIN14 | |||||

30 | E24 | UART2_TXD | 0 | weim | WEIM_D[26] | 3.3V | |

1 | ipu1 | DI1_PIN11 | |||||

2 | ipu1 | CSI0_D[1] | |||||

3 | ipu2 | CSI1_D[14] | |||||

4 | uart2 | TXD_MUX | |||||

5 | gpio3 | GPIO[26] | |||||

6 | ipu1 | SISG[2] | |||||

7 | ipu1 | DISP1_DAT[22] | |||||

32 | E25 | UART2_RXD | 0 | weim | WEIM_D[27] | 3.3V | |

1 | ipu1 | DI1_PIN13 | |||||

2 | ipu1 | CSI0_D[0] | |||||

3 | ipu2 | CSI1_D[13] | |||||

4 | uart2 | RXD_MUX | |||||

5 | gpio3 | GPIO[27] | |||||

6 | ipu1 | SISG[3] | |||||

7 | ipu1 | DISP1_DAT[23] | |||||

34 | D25 | UART3_CTS | 0 | weim | WEIM_D[23] | 3.3V | |

1 | ipu1 | DI0_D0_CS | |||||

2 | uart3 | CTS | |||||

3 | uart1 | DCD | |||||

4 | ipu2 | CSI1_DATA_EN | |||||

5 | gpio3 | GPIO[23] | |||||

6 | ipu1 | DI1_PIN2 | |||||

7 | ipu1 | DI1_PIN14 | |||||

36 | H21 | UART3_RTS | 0 | weim | WEIM_D[31] | 3.3V | |

1 | ipu1 | DISP1_DAT[20] | |||||

2 | ipu1 | DI0_PIN12 | |||||

3 | ipu1 | CSI0_D[2] | |||||

4 | uart3 | RTS | |||||

5 | gpio3 | GPIO[31] | |||||

6 | usboh3 | USBH1_PWR | |||||

7 | pl301_mx6q_ per1 | HPROT[1] | |||||

38 | F22 | UART3_TXD | 0 | weim | WEIM_D[24] | 3.3V | |

1 | ecspi4 | SS2 | |||||

2 | uart3 | TXD_MUX | |||||

3 | ecspi1 | SS2 | |||||

4 | ecspi2 | SS2 | |||||

5 | gpio3 | GPIO[24] | |||||

6 | audmux | AUD5_RXFS | |||||

7 | uart1 | DTR | |||||

40 | G22 | UART3_RXD | 0 | weim | WEIM_D[25] | 3.3V | |

1 | ecspi4 | SS3 | |||||

2 | uart3 | RXD_MUX | |||||

3 | ecspi1 | SS3 | |||||

4 | ecspi2 | SS3 | |||||

5 | gpio3 | GPIO[25] | |||||

6 | audmux | AUD5_RXC | |||||

7 | uart1 | DSR | |||||

42 | A23 | SD2_DATA2 | 0 | usdhc2 | DAT2 | 3.3V | |

1 | ecspi5 | SS1 | |||||

2 | weim | WEIM_CS[3] | |||||

3 | audmux | AUD4_TXD | |||||

4 | kpp | ROW[6] | |||||

5 | gpio1 | GPIO[13] | |||||

6 | ccm | STOP | |||||

44 | A22 | SD2_DATA0 | 0 | usdhc2 | DAT0 | 3.3V | |

1 | ecspi5 | MISO | |||||

3 | audmux | AUD4_RXD | |||||

4 | kpp | ROW[7] | |||||

5 | gpio1 | GPIO[15] | |||||

6 | dcic2 | DCIC_OUT | |||||

46 | C21 | SD2_CLK | 0 | usdhc2 | CLK | 3.3V | |

1 | ecspi5 | SCLK | |||||

2 | kpp | COL[5] | |||||

3 | audmux | AUD4_RXFS | |||||

4 | pcie_ctrl | DIAG_STATUS_BUS_MUX[9] | |||||

5 | gpio1 | GPIO[10] | |||||

6 | phy | DTB[1] | |||||

7 | sata_phy | DTB[1] | |||||

48 | B22 | SD2_DATA3 | 0 | usdhc2 | DAT3 | 3.3V | |

1 | ecspi5 | SS3 | |||||

2 | kpp | COL[6] | |||||

3 | audmux | AUD4_TXC | |||||

4 | pcie_ctrl | DIAG_STATUS_BUS_MUX[11] | |||||

5 | gpio1 | GPIO[12] | |||||

6 | sjc | DONE | |||||

50 | F19 | SD2_CMD | 0 | usdhc2 | CMD | 3.3V | |

1 | ecspi5 | MOSI | |||||

2 | kpp | ROW[5] | |||||

3 | audmux | AUD4_RXC | |||||

4 | pcie_ctrl | DIAG_STATUS_BUS_MUX[10] | |||||

5 | gpio1 | GPIO[11] | |||||

52 | E20 | SD2_DATA1 | 0 | usdhc2 | DAT1 | 3.3V | |

1 | ecspi5 | SS0 | |||||

2 | weim | WEIM_CS[2] | |||||

3 | audmux | AUD4_TXFS | |||||

4 | kpp | COL[7] | |||||

5 | gpio1 | GPIO[14] | |||||

6 | ccm | WAIT | |||||

54 | B14 | SATA_RXP |

| SATA</p| | SATA_RXP | 2.5V | |

56 | A14 | SATA_RXN |

| SATA_RXN | |||

58 | B12 | SATA_TXN |

| SATA_TXN | |||

60 | A12 | SATA_TXP |

| SATA_TXP | |||

62 | H20 | USB_OTG_OC | 0 | weim | WEIM_D[21] | 3.3V | |

1 | ecspi4 | SCLK | |||||

2 | ipu1 | DI0_PIN17 | |||||

3 | ipu2 | CSI1_D[11] | |||||

4 | usboh3 | USBOTG_OC | |||||

5 | gpio3 | GPIO[21] | |||||

6 | i2c1 | SCL | |||||

7 | spdif | IN1 | |||||

64 | E23 | USB_OTG_PWR_EN | 0 | weim | WEIM_D[22] | 3.3V | |

1 | ecspi4 | MISO | |||||

2 | ipu1 | DI0_PIN1 | |||||

3 | ipu2 | CSI1_D[10] | |||||

4 | usboh3 | USBOTG_PWR | |||||

5 | gpio3 | GPIO[22] | |||||

6 | spdif | OUT1 | |||||

7 | pl301_mx6q_ per1 | HWRITE | |||||

66 | B6 | USB_OTG_DN |

| USBOTG</p| | USB_OTG_DN | 2.5V | |

68 | A6 | USB_OTG_DP |

| USB_OTG_DP | |||

70 | E9 | USB_OTG_VBUS |

| USB_OTG_VBUS | 5V | ||

72 | T4 | USB_OTG_ID | 0 | esai1 | SCKR | 3.3V | |

1 | wdog2 | WDOG_B | |||||

2 | kpp | ROW[5] | |||||

4 | pwm2 | PWMO | |||||

5 | gpio1 | GPIO[1] | |||||

6 | usdhc1 | CD | |||||

7 | src | TESTER_ACK | |||||

74 | B2 | PCIE_RXP |

| PCIE</p| | PCIE_RXP | 2.5V | |

76 | B1 | PCIE_RXM |

| PCIE_RXM | |||

78 | B3 | PCIE_TXP |

| PCIE_TXP | |||

80 | A3 | PCIE_TXM |

| PCIE_TXM | |||

82 | D7 | CLK1_P |

| CLK1_P | |||

84 | C7 | CLK1_N |

| CLK1_N | |||

86 | K4 | HDMI_D2P |

| HDMI</p| | HDMI_D2P | 2.5V | |

88 | K3 | HDMI_D2M |

| HDMI_D2M | |||

90 | W4 | HDMI_CEC_IN |

| HDMI_CEC_IN | |||

92 | K1 | HDMI_HPD |

| HDMI_HPD | |||

94 | J4 | HDMI_D1P |

| HDMI_D1P | |||

96 | J3 | HDMI_D1M |

| HDMI_D1M | |||

98 | J6 | HDMI_CLKP |

| HDMI_CLKP | |||

100 | J5 | HDMI_CLKM |

| HDMI_CLKM | |||

102 | K6 | HDMI_D0P |

| HDMI_D0P | |||

104 | K5 | HDMI_D0M |

| HDMI_D0M | |||

106 | N5 | I2C1_SCL | 0 | ipu1 | CSI0_D[9] | 2.5V | |

1 | weim | WEIM_D[7] | |||||

2 | ecspi2 | MOSI | |||||

3 | kpp | ROW[7] | |||||

4 | i2c1 | SCL | |||||

5 | gpio5 | GPIO[27] | |||||

6 | mmdc | MMDC_DEBUG[48] | |||||

7 | ARM CortexA9 MPCore Platform | TRACE[6] | |||||

108 | N6 | I2C1_SDA | 0 | ipu1 | CSI0_D[8] | 2.5V | |

1 | weim | WEIM_D[6] | |||||

2 | ecspi2 | SCLK | |||||

3 | kpp | COL[7] | |||||

4 | i2c1 | SDA | |||||

5 | gpio5 | GPIO[26] | |||||

6 | mmdc | MMDC_DEBUG[47] | |||||

7 | ARM CortexA9 MPCore Platform | TRACE[5] | |||||

110 | N1 | AUD3_TXC | 0 | ipu1 | CSI0_D[4] | 2.5V | |

1 | weim | WEIM_D[2] | |||||

2 | ecspi1 | SCLK | |||||

3 | kpp | COL[5] | |||||

4 | audmux | AUD3_TXC | |||||

5 | gpio5 | GPIO[22] | |||||

6 | mmdc | MMDC_DEBUG[43] | |||||

7 | ARM CortexA9 MPCore Platform | TRACE[1] | |||||

112 | P2 | AUD3_TXD | 0 | ipu1 | CSI0_D[5] | 2.5V | |

1 | weim | WEIM_D[3] | |||||

2 | ecspi1 | MOSI | |||||

3 | kpp | ROW[5] | |||||

4 | audmux | AUD3_TXD | |||||

5 | gpio5 | GPIO[23] | |||||

6 | mmdc | MMDC_DEBUG[44] | |||||

7 | ARM CortexA9 MPCore Platform | TRACE[2] | |||||

114 | N3 | AUD3_RXD | 0 | ipu1 | CSI0_D[7] | 2.5V | |

1 | weim | WEIM_D[5] | |||||

2 | ecspi1 | SS0 | |||||

3 | kpp | ROW[6] | |||||

4 | audmux | AUD3_RXD | |||||

5 | gpio5 | GPIO[25] | |||||

6 | mmdc | MMDC_DEBUG[46] | |||||

7 | ARM CortexA9 MPCore Platform | TRACE[4] | |||||

116 | N4 | AUD3_TXFS | 0 | ipu1 | CSI0_D[6] | 2.5V | |

1 | weim | WEIM_D[4] | |||||

2 | ecspi1 | MISO | |||||

3 | kpp | COL[6] | |||||

4 | audmux | AUD3_TXFS | |||||

5 | gpio5 | GPIO[24] | |||||

6 | mmdc | MMDC_DEBUG[45] | |||||

7 | ARM CortexA9 MPCore Platform | TRACE[3] | |||||

118 | R7 | I2C3_SCL | 0 | esai1 | HCKR | 3.3V | |

1 | observe_mux | OBSRV_INT_OUT0 | |||||

2 | i2c3 | SCL | |||||

4 | ccm | CLKO2 | |||||

5 | gpio1 | GPIO[3] | |||||

6 | usboh3 | USBH1_OC | |||||

7 | mlb | MLBCLK | |||||

120 | T3 | I2C3_SDA | 0 | esai1 | SCKT | 3.3V | |

1 | observe_mux | OBSRV_INT_OUT1 | |||||

2 | i2c3 | SDA | |||||

3 | ccm | CCM_OUT_0 | |||||

4 | csu | CSU_INT_DEB | |||||

5 | gpio1 | GPIO[6] | |||||

6 | usdhc2 | LCTL | |||||

7 | mlb | MLBSIG | |||||

122 | T6 | CAN2_TX | 0 | can2 | TXCAN | 3.3V | |

1 | ipu1 | SISG[4] | |||||

2 | usboh3 | USBOTG_OC | |||||

3 | kpp | COL[4] | |||||

4 | uart5 | RTS | |||||

5 | gpio4 | GPIO[14] | |||||

6 | mmdc | MMDC_DEBUG[49] | |||||

7 | ARM CortexA9 MPCore Platform | HADDR[7] | |||||

124 | V5 | CAN2_RX | 0 | can2 | RXCAN | 3.3V | |

1 | ipu1 | SISG[5] | |||||

2 | usboh3 | USBOTG_PWR | |||||

3 | kpp | ROW[4] | |||||

4 | uart5 | CTS | |||||

5 | gpio4 | GPIO[15] | |||||

6 | mmdc | MMDC_DEBUG[50] | |||||

7 | pl301_mx6q_ per1 | HADDR[8] | |||||

126 | T5 | GPIO_0_CLKO | 0 | ccm | CLKO | 3.3V | |

2 | kpp | COL[5] | |||||

3 | asrc | ASRC_EXT_CLK | |||||

4 | epit1 | EPITO | |||||

5 | gpio1 | GPIO[0] | |||||

6 | usboh3 | USBH1_PWR | |||||

7 | snvs_hp_wrapper | SNVS_VIO_5 | |||||

128 | NC | GND |

|

|

| 0V | |

130 | AA2 | LVDS1_TX1_N |

| LVDS1</p| | LVDS1_TX1_N | 2.5V | |

132 | AA1 | LVDS1_TX1_P |

| LVDS1_TX1_P | |||

134 | Y2 | LVDS1_TX0_P |

| LVDS1_TX0_P | |||

136 | Y1 | LVDS1_TX0_N |

| LVDS1_TX0_N | |||

138 | AA3 | LVDS1_TX3_N |

| LVDS1_TX3_N | |||

140 | AA4 | LVDS1_TX3_P |

| LVDS1_TX3_P | |||

142 | AB2 | LVDS1_TX2_P |

| LVDS1_TX2_P | |||

144 | AB1 | LVDS1_TX2_N |

| LVDS1_TX2_N | |||

146 | Y3 | LVDS1_CLK_N |

| LVDS1_CLK_N | |||

148 | Y4 | LVDS1_CLK_P |

| LVDS1_CLK_P | |||

150 | A16 | NANDF_ALE | 0 | rawnand | ALE | 3.3V | |

1 | usdhc4 | RST | |||||

2 | pcie_ctrl | DIAG_STATUS_BUS_MUX[0] | |||||

3 | usboh3 | UH3_DFD_OUT[12] | |||||

4 | usboh3 | UH2_DFD_OUT[12] | |||||

5 | gpio6 | GPIO[8] | |||||

6 | mipi_core | DPHY_TEST_IN[24] | |||||

7 | tpsmp | HTRANS[1] | |||||

152 | C15 | NANDF_CLE | 0 | rawnand | CLE | 3.3V | |

1 | ipu2 | SISG[4] | |||||

2 | pcie_ctrl | DIAG_STATUS_BUS_MUX[31] | |||||

3 | usboh3 | UH3_DFD_OUT[11] | |||||

4 | usboh3 | UH2_DFD_OUT[11] | |||||

5 | gpio6 | GPIO[7] | |||||

6 | mipi_core | DPHY_TEST_IN[23] | |||||

7 | tpsmp | HTRANS[0] | |||||

154 | E15 | NANDF_WP_B | 0 | rawnand | RESETN | 3.3V | |

1 | ipu2 | SISG[5] | |||||

2 | pcie_ctrl | DIAG_STATUS_BUS_MUX[1] | |||||

3 | usboh3 | UH3_DFD_OUT[13] | |||||

4 | usboh3 | UH2_DFD_OUT[13] | |||||

5 | gpio6 | GPIO[9] | |||||

6 | mipi_core | DPHY_TEST_OUT[32] | |||||

7 | pl301_mx6q_per1 | HSIZE[0] | |||||

156 | D20 | SD1_CLK | 0 | usdhc1 | CLK | 3.3V | |

1 | ecspi5 | SCLK | |||||

2 | osc32k | 32K_OUT | |||||

3 | gpt | CLKIN | |||||

5 | gpio1 | GPIO[20] | |||||

6 | phy | DTB[0] | |||||

7 | sata_phy | DTB[0] | |||||

158 | U5 | I2C2_SCL | 0 | ecspi1 | SS3 | 3.3V | |

1 | enet | CRS | |||||

2 | hdmi_tx | DDC_SCL | |||||

3 | kpp | COL[3] | |||||

4 | i2c2 | SCL | |||||

5 | gpio4 | GPIO[12] | |||||

6 | spdif | IN1 | |||||

7 | pl301_mx6q_per1 | HADDR[5] | |||||

160 | T7 | I2C2_SDA | 0 | osc32k | 32K_OUT | 3.3V | |

1 | asrc | ASRC_EXT_CLK | |||||

2 | hdmi_tx | DDC_SDA | |||||

3 | kpp | ROW[3] | |||||

4 | i2c2 | SDA | |||||

5 | gpio4 | GPIO[13] | |||||

6 | usdhc1 | VSELECT | |||||

7 | pl301_mx6q_per1 | HADDR[6] | |||||

162 | U23 | DISP0_DAT19 | 0 | ipu1 | DISP0_DAT[19] | 3.3V | |

1 | ipu2 | DISP0_DAT[19] | |||||

2 | ecspi2 | SCLK | |||||

3 | audmux | AUD5_RXD | |||||

4 | audmux | AUD4_RXC | |||||

5 | gpio5 | GPIO[13] | |||||

6 | mmdc | MMDC_DEBUG[24] | |||||

7 | weim | WEIM_CS[3] | |||||

164 | U22 | DISP0_DAT20 | 0 | ipu1 | DISP0_DAT[20] | 3.3V | |

1 | ipu2 | DISP0_DAT[20] | |||||

2 | ecspi1 | SCLK | |||||

3 | audmux | AUD4_TXC | |||||

4 | sdma | DEBUG_EVT_CHN_LINES[7] | |||||

5 | gpio5 | GPIO[14] | |||||

6 | mmdc | MMDC_DEBUG[25] | |||||

7 | pl301_mx6q_ per1 | HADDR[28] | |||||

166 | R23 | DISP0_DAT6 | 0 | ipu1 | DISP0_DAT[6] | 3.3V | |

1 | ipu2 | DISP0_DAT[6] | |||||

2 | ecspi3 | SS3 | |||||

3 | audmux | AUD6_RXC | |||||

4 | sdma | DEBUG_RTBUFFER_WRITE | |||||

5 | gpio4 | GPIO[27] | |||||

6 | mmdc | MMDC_DEBUG[11] | |||||

7 | pl301_mx6q_ per1 | HADDR[17] | |||||

168 | T20 | DISP0_DAT21 | 0 | ipu1 | DISP0_DAT[21] | 3.3V | |

1 | ipu2 | DISP0_DAT[21] | |||||

2 | ecspi1 | MOSI | |||||

3 | audmux | AUD4_TXD | |||||

4 | sdma | DEBUG_BUS_DEVICE[0] | |||||

5 | gpio5 | GPIO[15] | |||||

6 | mmdc | MMDC_DEBUG[26] | |||||

7 | pl301_mx6q_per1 | HADDR[29] | |||||

170 | P23 | DISP0_DAT2 | 0 | ipu1 | DISP0_DAT[2] | 3.3V | |

1 | ipu2 | DISP0_DAT[2] | |||||

2 | ecspi3 | MISO | |||||

3 | usdhc1 | USDHC_DEBUG[2] | |||||

4 | sdma | DEBUG_MODE | |||||

5 | gpio4 | GPIO[23] | |||||

6 | mmdc | MMDC_DEBUG[7] | |||||

7 | pl301_mx6q_per1 | HADDR[13] | |||||

172 | R21 | DISP0_DAT10 | 0 | ipu1 | DISP0_DAT[10] | 3.3V | |

1 | ipu2 | DISP0_DAT[10] | |||||

3 | usdhc1 | USDHC_DEBUG[6] | |||||

4 | sdma | DEBUG_EVENT_CHANNE L[3] | |||||

5 | gpio4 | GPIO[31] | |||||

6 | mmdc | MMDC_DEBUG[15] | |||||

7 | pl301_mx6q_per1 | HADDR[21] | |||||

174 | P20 | DISP0_DAT4 | 0 | ipu1 | DISP0_DAT[4] | 3.3V | |

1 | ipu2 | DISP0_DAT[4] | |||||

2 | ecspi3 | SS1 | |||||

3 | usdhc1 | USDHC_DEBUG[4] | |||||

4 | sdma | DEBUG_BUS_RWB | |||||

5 | gpio4 | GPIO[25] | |||||

6 | mmdc | MMDC_DEBUG[9] | |||||

7 | pl301_mx6q_per1 | HADDR[15] | |||||

176 | GND | GND |

|

|

| 0V | |

178 | R2 | ENET_REF_CLK | 0 | esai1 | TX3_RX2 | 3.3V | |

1 | enet | 1588_EVENT2_IN | |||||

3 | usdhc1 | LCTL | |||||

4 | spdif | IN1 | |||||

5 | gpio7 | GPIO[11] | |||||

6 | i2c3 | SDA | |||||

7 | sjc | DE_B | |||||

180 | P6 | ENET_nINT | 0 | esai1 | TX1 | 3.3V | |

1 | enet | RX_CLK | |||||

2 | usdhc3 | VSELECT | |||||

3 | sdma | SDMA_EXT_EVENT[1] | |||||

4 | asrc | ASRC_EXT_CLK | |||||

5 | gpio7 | GPIO[13] | |||||

6 | snvs_hp_wrapper | SNVS_VIO_5_CTL | |||||

7 | src | SYSTEM_RST | |||||

182 | W22 | ENET_RXD1 | 0 | mlb | MLBSIG | 3.3V | |

1 | enet | RDATA[1] | |||||

2 | esai1 | FST | |||||

4 | enet | 1588_EVENT3_OUT | |||||

5 | gpio1 | GPIO[26] | |||||

6 | phy | TCK | |||||

184 | W23 | ENET_RX_ER | 0 | NO_NAME | USBOTG_ID | 3.3V | |

1 | enet | RX_ER | |||||

2 | esai1 | HCKR | |||||

3 | spdif | IN1 | |||||

4 | enet | 1588_EVENT2_OUT | |||||

5 | gpio1 | GPIO[24] | |||||

6 | phy | TDI | |||||

186 | V22 | ENET_nRST | 1 | enet | TX_CLK | 3.3V | |

2 | esai1 | FSR | |||||

3 | sdma | DEBUG_BUS_DEVICE[4] | |||||

5 | gpio1 | GPIO[23] | |||||

6 | spdif | SRCLK | |||||

188 | V23 | ENET_MDIO | 1 | enet | MDIO | 3.3V | |

2 | esai1 | SCKR | |||||

3 | sdma | DEBUG_BUS_DEVICE[3] | |||||

4 | enet | 1588_EVENT1_OUT | |||||

5 | gpio1 | GPIO[22] | |||||

6 | spdif | PLOCK | |||||

190 | U21 | ENET_CRS_DV | 1 | enet | RX_EN | 3.3V | |

2 | esai1 | SCKT | |||||

3 | spdif | SPDIF_EXTCLK | |||||

5 | gpio1 | GPIO[25] | |||||

6 | phy | TDO | |||||

192 | V21 | ENET_TX_EN | 1 | enet | TX_EN | 3.3V | |

2 | esai1 | TX3_RX2 | |||||

5 | gpio1 | GPIO[28] | |||||

6 | sata_phy | TDI | |||||

194 | W20 | ENET_TXD1 | 0 | mlb | MLBCLK | 3.3V | |

1 | enet | TDATA[1] | |||||

2 | esai1 | TX2_RX3 | |||||

4 | enet | 1588_EVENT0_IN | |||||

5 | gpio1 | GPIO[29] | |||||

6 | sata_phy | TDO | |||||

196 | W21 | ENET_RXD0 | 0 | osc32k | 32K_OUT | 3.3V | |

1 | enet | RDATA[0] | |||||

2 | esai1 | HCKT | |||||

3 | spdif | OUT1 | |||||

|

| 5 | gpio1 | GPIO[27] | |||

6 | phy | TMS | |||||

198 | V20 | ENET_MDC | 0 | mlb | MLBDAT | 3.3V | |

1 | enet | MDC | |||||

2 | esai1 | TX5_RX0 | |||||

4 | enet | 1588_EVENT1_IN | |||||

5 | gpio1 | GPIO[31] | |||||

6 | sata_phy | TMS | |||||

200 | U20 | ENET_TXD0 | 0 | enet | TDATA[0] | 3.3V | |

1 | esai1 | TX4_RX1 | |||||

5 | gpio1 | GPIO[30] | |||||

6 | sata_phy | TCK | |||||

- A9 Processor 5 Pieces / (Min. Order)

- Cortex A7 5 Pieces / (Min. Order)

- Imx6ul Board 5 Pieces / (Min. Order)

- Imx6ul 5 Pieces / (Min. Order)

- I.mx28 Board 5 Pieces / (Min. Order)

- I.mx28 5 Pieces / (Min. Order)

Favorites

Favorites